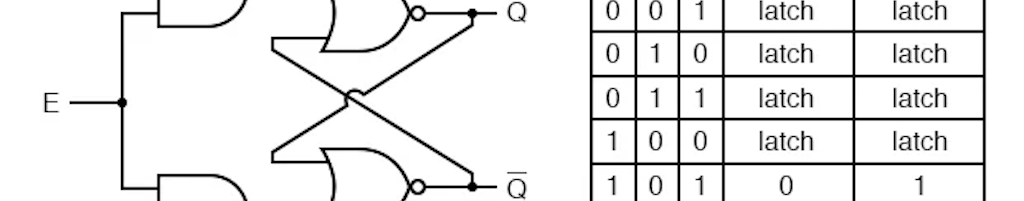

SR Latch

This page is more than 10 years old and besides the fact that the circuit diagrams are no longer available, it needs some love. I intent to clean it up in the near future, so keep posted…

While studying for my Digital Electronics and Processors exam ↗ I came across the SR Latch, the Set-Reset Latch. It is a sequential circuit that is capable of storing 1 bit and it forms the basis for Flip-flops and memory in general.

A SR Latch can be constructed using two NOR ports and by chance I had some NOR ports lying around…

The circuit

We want a circuit that can memorize 1 bit. So we need a circuit that allows us to set or reset a bit and also lets us consult that value. Because our stimulus is not constantly present, the circuit needs to constantly feed its own value. This can be achieved by introducing feedback.

The conceptual circuit below shows two NOR gates that use each others’ output. This way when no set or reset signal is present, the feedback loop retains the memorized state.

Let’s see what happens. When set and reset are low the NOR ports will depend on each others’ output to come up with output. Due to noise they will in the end produce output. The outcome of this race will be is completely random, so let’s say that the output of NOR0 is 1.

That means that in1 of NOR1 is high and the output of NOR1 will become 0. Which is great, because both inputs of NOR0 must be 0 to produce an output of 1.

Q’ is in fact Q inverted, so everything matches and we have a stable state.

When we put set high, the inputs of NOR0 differ and the output becomes 0, which goes to the other NOR gate, which now will produce 1. Which is indeed the value we just set.

Now when we bring set back low, the inputs of NOR0 are 0 and 1, so the gate still produces 0 and everything remains stable. The circuit can memorize 1 bit.

The schematic

To actually create this circuit, I used a Texas Instruments SN74LS27N ↗. This IC contains 3 3-input NOR gates, so it’s a bit more that I needed, but it was what I had laying around. The three gates are labeled 1 to 3 and the inputs on each gate are labeled A through C, while the output is labeled Y. I’m using gates 1 and 2.

Set and reset are two SPST switches and on the output side, two LEDs are showing the state of Q and Q’.

Note that the third input of each used gate must be connected to GND.

vCard

vCard

Homemade by CVG

Homemade by CVG

My Homemade Apps

My Homemade Apps

Thingiverse

Thingiverse

Strava

Strava